发布时间:2025-12-10 来源:半导体产业报告

DRAM 正站在 10nm 级节点的临界点。D1z、D1a 到 D1b 的推进,不仅意味着几何尺寸的进一步压缩,更是工艺路径与材料体系的重新分野。EUV 与多重图形化短期内并行,电容介质进入 NbO/ZrNbO 的组合时代,外围晶体管全面转向 HKMG,行业的技术博弈已进入微米之下的细节角逐。

在产品层面,算力需求的爆发正驱动新一代存储快速落地:Samsung 首发 GDDR7,SK hynix 将 HBM3E 带入 NVIDIA Blackwell 平台,移动端与通用计算则由 16Gb LPDDR5X 与 DDR5 系列承载出货。高比特产出的 DDR/LPDDR 与高价值密度的 HBM/GDDR,正在形成泾渭分明的双赛道格局。

全球三大厂商的技术差距被压缩至“个位数纳米”,而 CXMT 通过 16Gb DDR5-6000 已进入对标体系。可以说,当前 DRAM 的竞争已超越节点名称,真正的核心是:谁能率先在产品落地中兑现微缩红利,并在比特与价值密度之间找到最优解。

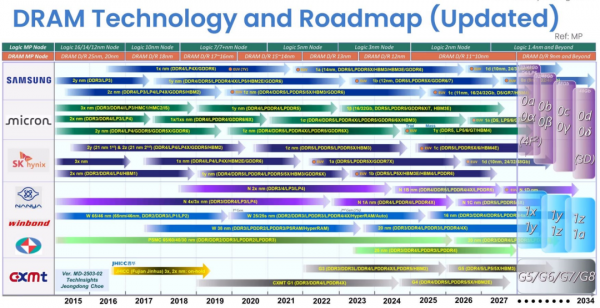

过去五年,DRAM 工艺节点的演进从 D1x、D1y、D1z,逐步进入 D1a(约 14nm)、D1b(约 12nm)、D1c(约 11nm),直至 D1d(约 10nm)时代。伴随节点持续下探,DRAM 的产品矩阵同步跨越,从 DDR4/LPDDR4X/GDDR6,全面迈向 DDR5、LPDDR5X、GDDR7,以及 HBM3/3E。这一进程不仅意味着比特密度与能效的线性提升,更意味着带宽与架构能力的非线性跃迁。资本开支暴增背后,是全球算力军备竞赛的全面爆发。

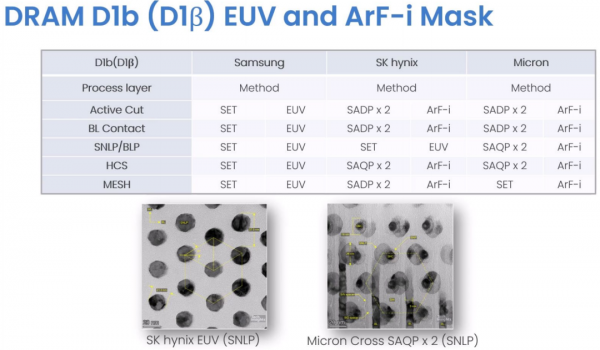

技术路径的分化尤为显著。SK hynix、Samsung 等领先厂商在 D1b 节点已明确导入 EUV 光刻,而部分厂商则继续依赖多重图形化延伸工艺窗口。在这一关键阶段,EUV 的介入已不仅是技术升级,更是产业分水岭:它决定了工艺复杂度与良率的临界点,也决定了谁能在高性能计算与 AI 时代占据主动权。

在产品端,三星已率先推出业界首款 GDDR7 芯片(D1z、8Gb),为下一代 GPU 平台提供支撑。这一里程碑式产品标志着图形显存正式进入 GDDR7 世代,验证了高频与能效的新基线。另一方面,HBM 路线则快速迈入 HBM3E。SK hynix 最新 8Hi 堆叠的 HBM3E,将核心 die 从 16Gb(D1z)提升至 24Gb(D1b),在堆高不变的情况下实现容量跃升,并已服务于 NVIDIA Blackwell HGX B200 平台。这种“堆高不变、密度跃升”的模式,将 HBM 从高端 HPC 推向更广泛的 AI 训练与推理市场。

总体来看,10nm 级 DRAM 技术演进与产品落地呈现三大特征:其一,工艺路线双轨并进,EUV 与多重图形化短期内并存;其二,产品谱系全面升级,GDDR7 与 HBM3E 同步进入量产,拉动新一轮高性能计算需求;其三,产业竞争格局进一步集中,领先厂商通过节点与产品双重突破,强化市场壁垒。换言之,10nm 级 DRAM 已不只是制程的数字游戏,而是全球算力产业的“核武竞赛”。

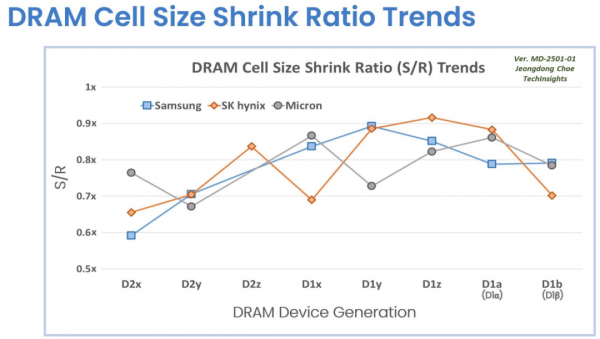

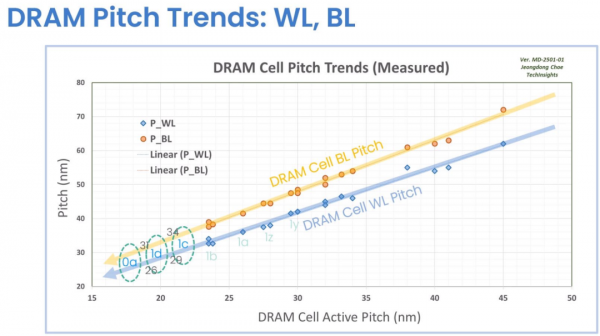

DRAM 的性能与成本演进,本质上取决于存储单元的缩小能力。随着制程进入 10nm 级,Cell Size 的收缩已经不再依赖单一方向,而是由 缩小率(Shrink Ratio, S/R)与 Pitch 收敛双重驱动。换句话说,DRAM 厂商的竞争不只是“几纳米的节点差距”,而是对主动区、字线、位线三大关键 Pitch 的全方位博弈。

在主动区(Active Area)与字线(Word Line, WL),缩减主要来自“宽度”的压缩;而在位线(Bit Line, BL),则更多依赖“间距”的收窄。这种“宽度压缩 + 间距收缩”的路径,使得存储单元能够在保持电气稳定性的同时继续缩小。具体来看,WL/BL 的 Pitch 演进已逼近物理极限,每一次缩减都需要叠加多重图形化或 EUV 曝光技术的支撑。

S/R 的改善趋势清晰:在 D1z 至 D1b 的代际过渡中,Shrink Ratio 显著提升,意味着相同晶圆面积下可实现更高比特产出。对于厂商而言,这一指标的改善直接决定了成本曲线的斜率与盈利空间。某种程度上,S/R 的提升甚至比节点名称更具“含金量”——它决定了厂商能否在相似节点下实现差异化的比特经济学。

值得注意的是,制程演进也带来了版图设计上的新矛盾:一方面,Pitch 的极限缩减要求更激进的图形方案,另一方面,电容保持时间与信号干扰的挑战却日益突出。正因如此,10nm 级的版图演进已经不再是“单纯缩小”,而是“在稳定性与密度之间的精密平衡”。这一平衡点,决定了不同厂商能否在量产中实现良率与性能的双赢。

简而言之,DRAM 的版图演进已经进入“毫米级微调、纳米级博弈”的阶段。主动区、字线、位线的 Pitch,每一个几纳米的缩减背后,都是对光刻、材料与架构的全方位考验。行业进入 D1b 时代,版图不只是工艺的产物,更是竞争战略的缩影。

10nm 级 DRAM 已经进入“工艺与材料的双重分水岭”。节点不再仅靠几何缩小支撑,而是通过 图形化方式、介质体系与外围晶体管架构的系统性升级,共同推动比特密度与可靠性的提升。

首先,在图形化路径上,D1b 成为 EUV 与多重图形化的交汇点。SK hynix 已在 D1b 节点采用 EUV(Self-Aligned Negative Litho Process, SNLP),以减少掩模层数并提高关键线宽的一致性;而 Micron 则继续沿用 Cross SAQP×2(自对准四重图形化),在既有工艺窗口内深挖潜力。这意味着,短期内业界存在两条并行路线:一条依赖 EUV 突破复杂度,另一条依赖多重图形化延长既有设备寿命。工艺路径的选择不仅体现技术能力,更反映资本支出与风险偏好。

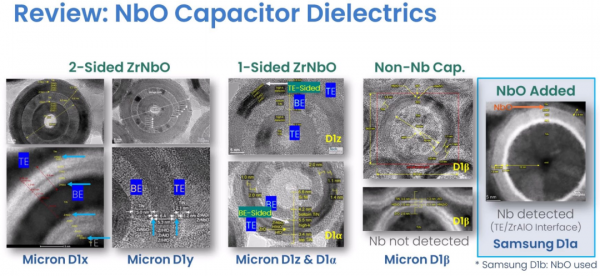

其次,在电容介质体系上,厂商逐渐从单一 NbO 转向 NbO/ZrNbO 的多元化组合,不同厂商在电容侧壁采用“单侧/双侧”构型,直接影响存储单元的阈值分布与漏电控制。与之匹配的 Poly-Si/TiN 双功函数电极设计,进一步帮助控制功率和可靠性。在这个维度上,材料工程已经成为工艺竞争的关键变量:谁能在可靠性与比特密度之间找到最佳平衡,谁就能在节点微缩中抢占先机。

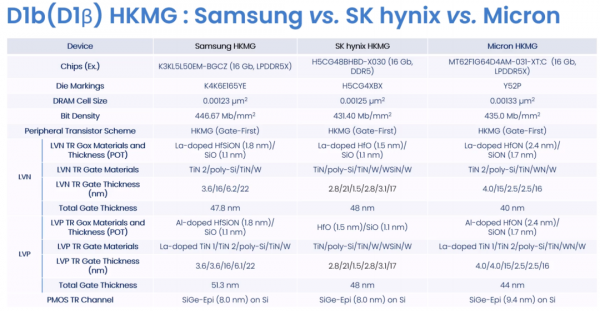

第三,外围晶体管架构全面转向高介电金属栅(HKMG),已成为行业共识。在此之上,PMOS 的 SiGe 外延厚度出现差异:Samsung、SK hynix 约为 8.0nm,而 Micron 约为 9.4nm。看似微小的厚度差异,实则决定了功耗与性能的平衡点。这种“纳米级的微调”正成为厂商差异化的重要来源。

归纳来看,10nm 级 DRAM 工艺竞争已不再是单维度的“光刻之争”,而是 图形化路线 + 材料体系 + 外围晶体管的“三维对比”。EUV 的渗透速度、电容材料的选择与 PMOS 外延厚度的取舍,共同决定了谁能在性能、良率、成本三角中实现最佳均衡。用一句话概括:在 10nm 级 DRAM,工艺路径已成为战略抉择,材料细节则是胜负手。

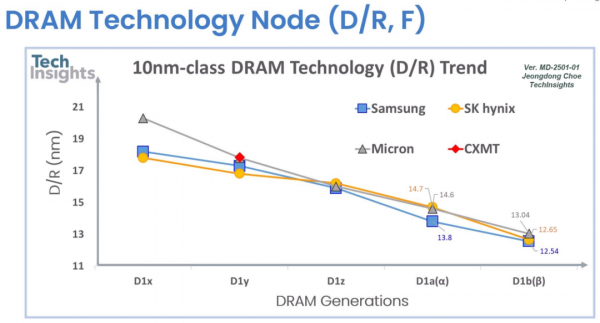

在 10nm 级 DRAM 的竞争中,厂商之间的差距已压缩至“个位数纳米”。无论是线宽(D/R 指标)还是电容构型,竞争已进入微缩极限下的细节较量。

首先,从 D/R 指标来看,SK hynix、Samsung、Micron 与长鑫(CXMT)已经在 10nm 级展开正面对标。其中,国际三大厂商(Samsung、SK hynix、Micron)在 D1z 至 D1b 代际保持极小差距,展现出接近同步的推进节奏。相比之下, CXMT 则通过快速爬坡缩小差距,其最新 16Gb DDR5-6000 已进入对比序列。这一突破不仅意味着国产厂商在高带宽应用上实现“代际追平”,更体现出其在光刻、材料和电容设计上的积累逐步显现。

在电容材料与外围工艺方面,厂商差异更加明显。国际厂商已全面采用 HKMG 架构,并在 SiGe 外延厚度上展现差异化——Samsung 与 SK hynix 约为 8.0nm,而 Micron 选择 9.4nm。这背后是不同厂商在性能与功耗之间的取舍逻辑:前者偏重性能释放,后者则倾向于功耗控制与良率保障。与此同时,电容介质 NbO/ZrNbO 的不同侧向构型,也反映出各厂在可靠性与密度之间的战略偏好。

总体而言,全球 DRAM 技术格局进入“三强鼎立 + 中国追赶”的新阶段。三大国际厂商在节点、材料与架构上的演进保持高度接近,竞争重心转向“细节最优”;而 CXMT 通过 DDR5-6000 的实证进入对比样本,标志着国产厂商首次在核心产品上进入第一梯队的讨论范围。未来数年,全球 DRAM 竞争将不仅是节点之争,更是材料体系与比特经济学的系统较量。

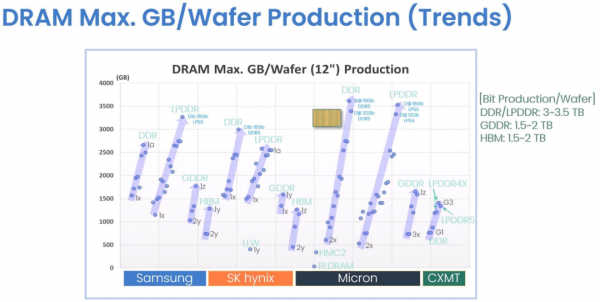

在 DRAM 产业链中,“每片晶圆可产出的最大比特数”是衡量经济性的核心指标之一。它不仅决定单片成本,还直接影响资本回报率和产品定价权。

从数据来看,DDR 与 LPDDR 的比特产出区间最高,单片晶圆可实现 3~3.5TB 的比特容量;相比之下,GDDR 与 HBM 的比特产出相对有限,仅在 1.5~2TB 区间。这种差异并非工艺不足,而是产品定位与价值逻辑的不同:DDR/LPDDR 面向高出货量、低成本敏感型市场,需要极致的比特密度以摊薄成本;而 GDDR 与 HBM 则属于“带宽优先”,更强调系统性能的溢价能力。

由此可见,比特经济学在不同产品族中呈现出两极化趋势:一端是 DDR/LPDDR 的规模驱动,通过高密度实现低成本扩展;另一端是 HBM/GDDR 的性能驱动,依靠带宽溢价锁定高附加值市场。前者追求的是“比特最大化”,后者追求的则是“价值密度最大化”。

这种分化趋势与算力需求结构高度契合。AI 训练与高性能计算推动 HBM/GDDR 需求激增,市场对“带宽溢价”的接受度显著提升;而在 PC、移动与服务器通用内存中,DDR/LPDDR 依然以成本为核心逻辑,确保出货规模与市场覆盖率。资本开支的投入方向也在呼应这一分化:先进产线逐步向 HBM/GDDR 倾斜,而成熟产能则继续服务 DDR/LPDDR 的大规模生产。

换句话说,DRAM 产业已经分裂为两条清晰赛道:一条是 DDR/LPDDR 的“比特规模逻辑”,另一条是 HBM/GDDR 的“带宽溢价逻辑”。前者以产出极限换取成本优势,后者则用系统性能锁定利润洼地。未来的盈利能力,将取决于厂商能否在比特与价值密度之间找到最优平衡点。

2025 年下半年,DRAM 技术观察的重点已经清晰:节点继续迈向 D1b 与 D1c,EUV 的渗透程度将成为行业分水岭;在产品端,HBM3E、GDDR7 与高频 LPDDR5X 将持续主导话题,成为市场验证新技术与新材料的最佳样本。

从工艺演进看,未来的关注点在于 EUV 与多重图形化的博弈。随着掩模复杂度和良率挑战的加剧,EUV 的渗透已不再是“可选项”,而是“必答题”。然而,对于资本开支相对保守的厂商,多重图形化依旧是延续生产线寿命的重要路径。下半年,相关拆解将揭示不同厂商在工艺选择上的真实取舍。

在产品层面,HBM3E 已通过 NVIDIA Blackwell 平台完成市场落地,其“同堆高、密度提升”的模式将成为行业标杆。与此同时,GDDR7 已由 Samsung 首发量产,预计将快速进入高端 GPU 市场。移动端则以 16Gb LPDDR5X 为主力,厂商将在速率、功耗与封装形态上展开持续优化。这些产品将构成下半年技术追踪的核心样本库。

从竞争格局看,三大国际厂商在先进节点上的差距极小,核心观察点在于细节最优:电容材料体系的选择、SiGe 外延厚度的取舍、EUV 的层数控制。国产厂商 CXMT 则已凭借 16Gb DDR5-6000 进入对比序列,下半年能否在更高代际产品中保持节奏,将是观察其追赶路径的关键。

总体而言,2025 年下半年 DRAM 的分析工作将围绕三条主线展开:

节点与工艺 —— D1b/D1c 节点下 EUV 的渗透与图形化方案对比;

产品与市场 —— HBM3E、GDDR7 与 LPDDR5X 的性能与应用验证;

厂商格局 —— 三强鼎立下的细节差异,以及 CXMT 的代际追赶进展。

一句话总结:未来半年,DRAM 的焦点不在于“是否微缩”,而在于“如何微缩”与“谁能先在关键产品上兑现”。