发布时间:2025-11-11 来源:半导体行业观察

如台积电所说,直接硅基液冷(Direct-to-silicon liquid cooling)技术在应对高性能计算/人工智能应用中由2.5D/3D先进封装带来的高功率和高功率密度方面展现出巨大潜力。

在本文中,台积电的工程师在3.3倍光刻CoWoS-R封装上演示了一种基于硅的液冷解决方案——硅集成微型冷却器(IMC-Si)。该集成方案仅需对现有的CoWoS工艺流程进行少量修改。在硅逻辑芯片和液冷歧管盖之间涂覆了一种抗翘曲密封剂,形成用于直接液冷的防漏气室。该集成系统使用40℃水作为冷却剂,在10 LPM的流速下,能够均匀散热高达3.4 kW(在1.6倍光刻SoC上为2.5 W/mm²)的功率。

采用源自典型数据中心环境的临界水泄漏率 115 cc/year (氦气泄漏率为 4.4 x 10⁻⁶ Pa·m³/s)来评估密封剂的稳健性和可靠性。实验结果表明,该集成系统通过了包括多次回流焊(3 个循环)、热循环测试(2000 个循环)和高温超导测试(150 °C,1000 小时)在内的压力测试,氦气泄漏率至少比临界泄漏率低一个数量级。

此外,还进行了加速液体浸没测试(150 °C,4.8 bar 压力),以评估密封剂的抗液体泄漏性能。首次成功证明,与 IMC-Si 集成的 CoWoS 是一种可行的解决方案,能够满足日益苛刻的高性能计算/人工智能应用中对热性能和电性能的要求。

引言

最先进的人工智能 (AI) 模型飞速发展,导致模型规模的增长速度远远超过了摩尔定律。为了跟上步伐,异构集成各种芯片已成为超越传统逻辑扩展性能提升的必要手段。通过将逻辑和存储器集成在中介层上,可以显著缩小它们之间的距离,从而通过提高能效和带宽来增强计算性能。芯片的 3D 堆叠(例如 TSMC 的 SoIC)由于垂直方向上芯片间距的显著减小,能够提供更大的性能提升。

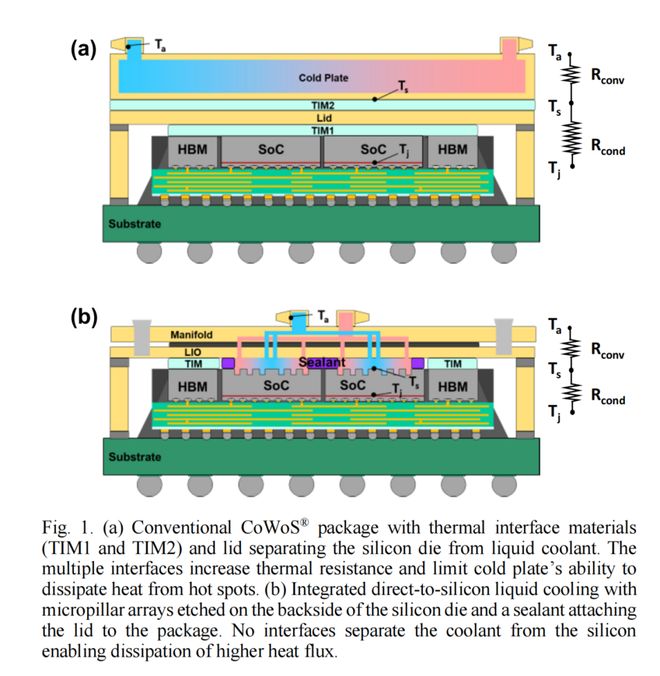

然而,集成系统在高功率密度下散热的能力限制了异构集成未来性能的提升。最简单的情况是,垂直堆叠两个逻辑芯片会使功率密度翻倍。近年来,液冷板因其优于风冷的散热效率而被集成到高性能计算 (HPC) 应用中。然而,如图 1(a) 所示,它们的间接液体冷却方案(包括沿传热路径的热界面材料 (TIM))限制了其在高功率密度应用中的冷却效率。

直接硅液冷技术通过将液态冷却剂直接输送到硅芯片背面来解决这一问题,如图 1(b) 所示。多项研究证实,直接硅液冷技术比传统冷板具有更高的功率密度。我们之前关于硅集成微型冷却器 (IMC-Si) 的研究表明,该冷却器采用直接液冷技术,在集成于 0.8 倍光罩热测试芯片 (TTV) 硅背面的交错微柱阵列上进行冷却,在均匀热通量下,其冷却能力可高达 2 kW,相当于 3.2 W/mm² 的功率密度。此外,在 1 kW 背景加热的情况下,该冷却器还能将局部热点冷却至 18 W/mm²。

尽管直接硅液冷技术比传统冷板具有更高的冷却能力,但其在数据中心的部署需要与现有异构集成系统兼容,并在各种环境条件下具备强大的防漏可靠性。大多数高性能计算 (HPC) 应用采用台积电的晶圆基芯片封装 (CoWoS) 平台,以实现大尺寸中介层,从而为多个芯片组提供高密度互连和高带宽的芯片间通信。

直接硅液冷解决方案必须证明其与 CoWoS 平台兼容,才能在未来的数据中心部署中得到应用。以往的直接硅液冷演示并未强调其与先进封装的兼容性,并且采用了不适用于大规模生产的液体密封机制。这些演示通常使用垫片或 O 形圈进行固体密封,但由于翘曲和拓扑结构变化的增加,这些密封方式难以扩展到更大的封装尺寸。

我们之前在 IMC-Si 方面的工作为与 CoWoS 平台的集成指明了方向,即使用可分散的聚合物基粘合剂作为逻辑芯片和歧管盖之间的密封剂。这种弹性体密封剂可以有效缓解大尺寸封装中的翘曲变化,并有助于多芯片密封。

本研究首次成功地将直接硅基液冷解决方案 IMC-Si 集成到 3.3X CoWoS-R 封装上。该集成系统使用 40 °C 水作为冷却剂,在 10 LPM 的流速下,可为逻辑芯片(1.6X 光罩)提供 3.4 kW 的冷却功率,并实现 2.5 W/mm² 的均匀热通量。将 IMC-Si 集成到 CoWoS平台上仅需对现有的 CoWoS工艺流程进行少量修改。此外,该集成封装在各种加速应力条件下(包括多次回流焊、温度循环 (TCG) 和高温存储 (HTS))均表现出良好的抗液漏性能。我们还验证了密封剂在高温高压条件下长时间浸液后仍能有效防止液漏。这项工作为未来在高性能计算 (HPC) 数据中心部署集成 IMC-Si 和 CoWoS 平台的封装奠定了基础。

集成 3.3 倍 CoWoS-R 平台

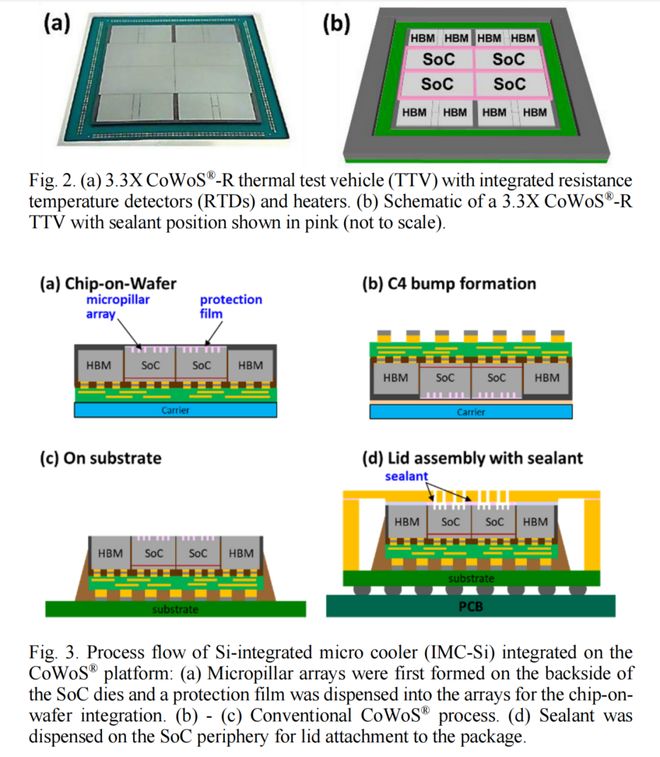

我们所提出的直接硅液冷解决方案 IMC Si 集成于 CoWoS-R 平台上。CoWoS-R 架构的主要优势之一是能够在保持高集成度的同时缩小封装尺寸。有机中介层起到应力缓冲作用,通过缓解热失配并改善热循环条件下的焊点和互连完整性,从而提高机械可靠性。如图 2(a) 所示,采用 3.3 倍 CoWoS-R TTV 封装模拟中心包含 4 个逻辑系统芯片 (SoC) 芯片、外围包含 8 个高带宽存储器 (HBM) 芯片的结构。

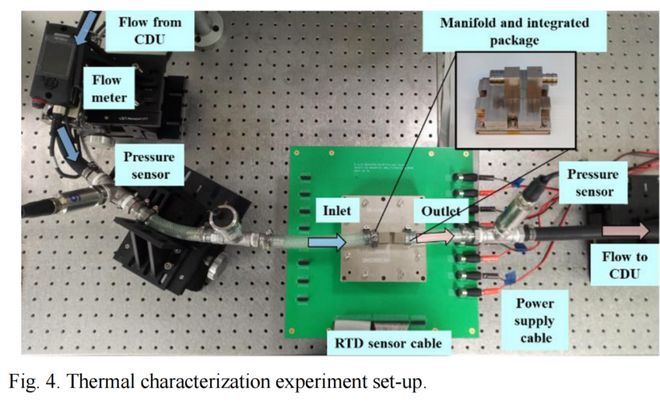

如图 3 所示,将 IMC-Si 集成到 3.3X CoWoS-R 封装上仅需对现有的 CoWoS-R 工艺流程进行极小的改动。该工艺流程首先在 SoC 背面形成微柱阵列,然后在阵列中涂覆一层保护膜。该保护膜符合传统 CoWoS-R 工艺流程中的热预算,且移除后不留任何残留物。之后,如图 2(b) 所示,在每个 SoC 的外周涂覆一层弹性密封剂。然后,将带有多个与每个 SoC 腔室对齐的进出气口的盖子连接到封装上。与传统的覆盖整个封装表面的导热界面材料 (TIM) 不同,该密封剂以一维线的形式涂覆在每个 SoC 芯片的周边。这种结构使得密封剂能够更好地适应大尺寸封装的翘曲,同时保持盖子和 SoC 之间良好的物理接触。回流焊后,将一个具有单个进出口的歧管组装到集成系统上,该歧管旨在实现多个冷却隔室之间的均匀流量分配。

热测试结果

A. 实验装置

3.3X CoWoS-R 封装包含两种尺寸的 TTV:13.0 x 25.9 mm² 的芯片用于模拟 SoC 芯片,11.0 x 11.0 mm² 的芯片用于模拟 HBM 芯片。采用开尔文型电阻温度检测器 (RTD) 监测温度变化。RTD 在温度控制良好的烘箱中进行校准。RTD 温度系数的平均值和标准偏差分别为 3.8 x 10⁻³ 和 9.0 x 10⁻⁶。每个 SoC 芯片上有五个 RTD;四个位于芯片的四个角,一个位于芯片的中心。由于密封剂的覆盖和液体流动停滞,预计每个 SoC 芯片的四个角区域的结温 (Tj,max) 最高。

热特性实验是在闭环配置中,使用商用数据中心冷却分配单元 (CDU) 进行的,如图 4 所示。入口处使用 40 °C 的纯水作为液体冷却剂,入口冷却剂与 Tj,max 之间的允许温差 (ΔT) 设置为 60 °C。

B. 均匀加热

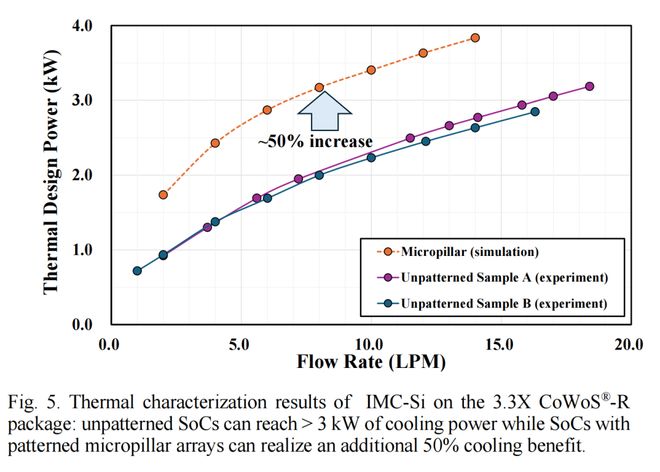

图 5 展示了 3.3X CoWoS-R 封装上 IMC Si 在不同流速下均匀热流的热特性测试结果。在总流速为 5.6 LPM(每个 SoC 约 1.4 LPM)的情况下,直接对 SoC 背面(未图案化,且无微柱阵列)进行硅液冷,四个 SoC 的总冷却能力可达 1.7 kW。由于无需 TIM 层及其相关的热阻,冷却液能够更有效地散热。此外,在达到“收益递减”点之前,通过 IMC-Si 进行直接液冷可以提升较高的流速下的散热性能,之后流速的进一步提升带来的收益将非常有限。当总流速提升至 11.5 LPM 时,TDP 提升至 2.5 kW,功率密度达到 1.9 W/mm²。相比之下,间接冷却系统(例如冷板)在流量显著降低的情况下,其热性能往往就会达到饱和。间接液体冷却系统的总热阻受限于多个中间表面的传导热阻。

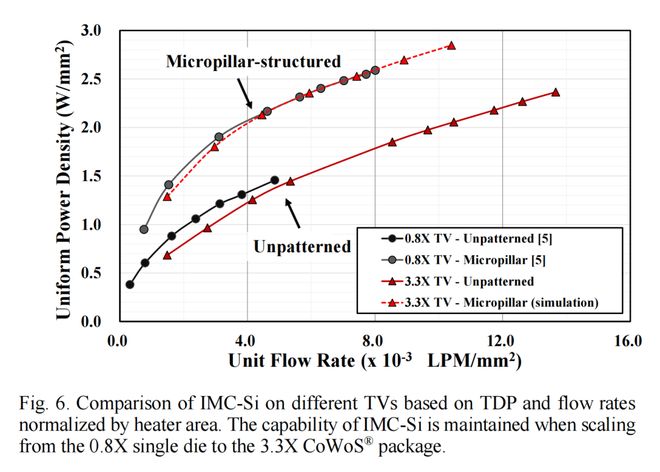

此外,仿真结果表明,如图 5 所示,集成在 SoC 背面的微柱阵列可额外提升 50% 的散热性能。这种提升归因于表面积的增加和湍流的产生。在 10 LPM 的流速下,TDP 可提升至 3.4 kW,从而实现 2.5 W/mm² 的功率密度。我们之前对集成在 0.8X TTV 上的 IMC-Si 的热特性分析结果也支持这一发现。图 6 通过将 TDP 和流速除以加热器面积或单位流速,比较了 0.8X TTV 和 3.3X CoWoS-R TTV 的热性能。对于未图案化表面上的 IMC-Si 液冷,0.8X TTV 和 3.3X TTV 的性能曲线相似。例如,在单位流速为 5 x 10⁻³ LPM/mm² 时,两种 TTV 的功率密度约为 1.5 W/mm²。当在 SoC 背面形成微柱阵列时,3.3X TV 的仿真结果与 0.8X TV 的实验数据几乎完全重合。这表明,从 0.8X 单芯片扩展到 3.3X CoWoS 平台时,IMC-Si 的冷却能力得以保持。

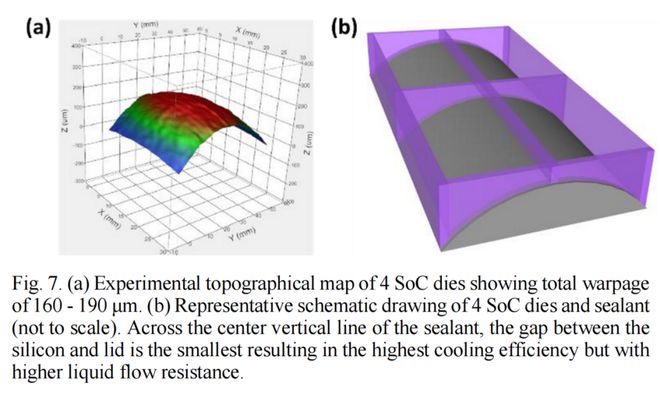

如图 7(a) 所示,封装尺寸较大以及多种材料集成导致的热膨胀系数 (CTE) 不匹配,使得 3.3X CoWoS-R TTV 中的四个 SoC 芯片出现 160-190 µm 的翘曲。在传统的带冷板封装中,这种翘曲通常会导致导热界面材料 (TIM) 覆盖不良或分层,从而降低其冷却性能。然而,IMC-Si 中的弹性体密封剂可以缓解翘曲引起的冷却问题。SoC 与盖板之间的间隙大小对流体动力学和冷却效率的影响截然不同。间隙越小,流动阻力越大;然而,由于更有效的传热路径,冷却效率反而会提高。如图 7(b) 所示,在靠近中心垂直密封线的位置,间隙较小,流动阻力较高,但冷却效率更高。相反,在边缘处,间隙可增大 160-190 µm,导致流动阻力降低,但冷却效率也随之降低。

封装可靠性表征

A. 用于早期可靠性测试的氦气泄漏测试

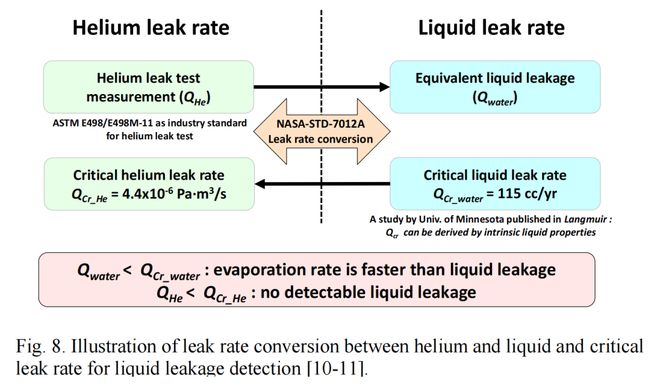

为了对 IMC-Si 集成 CoWoS-R 封装进行早期可靠性测试,我们按照标准的 JEDEC 封装可靠性测试方法评估了密封剂的防泄漏性能,并进行了额外的高压高温液体浸没测试。鉴于 IMC-Si 液冷技术的创新性,目前尚无成熟的可靠性表征方法。我们参考了数据中心行业组织开放计算项目 (OCP) 的液冷板可靠性测试指南,作为直接硅液冷的模板。根据 OCP 指南,由于氦气分子尺寸小,可以识别极小的针孔泄漏,因此推荐使用氦气进行泄漏检测 ]。此外,我们参考了 NASA 标准 NASA-STD-7012A,对氦气泄漏率和液体泄漏率进行了保守的换算:

其中,QF 为液体泄漏率,QHe 为氦气泄漏率,PINT 和 PEXT 分别为液体 (F) 和氦气 (He) 的内压和外压,VF 为氦气与液体的动态粘度比,P0 为大气压。

图 8 概述了氦气泄漏测试中泄漏率阈值(或临界泄漏率)的推导过程。为了检测液体泄漏,液体泄漏率必须超过典型数据中心环境下的蒸发速率。Extrand 等人解释说,该临界泄漏率可以根据液滴体积、接触角和流体固有特性计算得出,如公式 (2) 所示:

其中 γ 为表面张力,ρ 为密度,g 为重力加速度,φ 为接触角,D 为液体扩散系数,Cs 和 C∞ 分别为空气和环境空气中饱和蒸汽的浓度。利用该公式,数据中心的临界泄漏率 (Qcr_water) 估计为 115 cc/year(水)。Qcr_water 可以转换为临界氦泄漏率 (Qcr_He),其值为 4.4 x 10⁻⁶ Pa·m³/s。换句话说,如果集成封装的氦气泄漏测试结果小于 Qcr_He,则表明不会发生可检测到的液体泄漏。

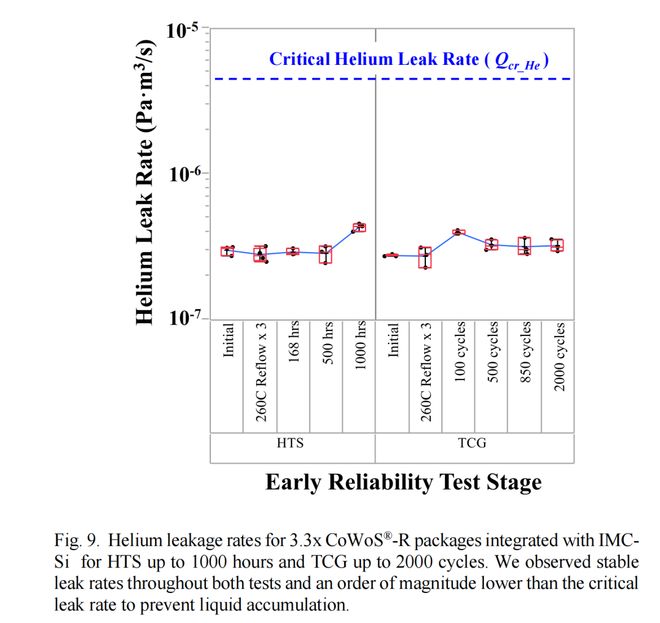

为了对IMC-Si集成3.3X CoWoS-R封装进行氦气泄漏测试,我们为封装组装了一个特制的单开口盖和歧管。除密封区域外,所有可能的泄漏路径均使用垫片和O型圈密封,以确保氦气泄漏仅通过密封剂发生。我们向封装内泵入1 bar的纯氦气作为示踪气体,以识别可能导致部署过程中水渗出的潜在泄漏点。氦气泄漏检测器检测到了通过密封剂的任何氦气泄漏。我们对样品进行了标准JEDEC可靠性测试流程的典型阶段测试,包括初始组装、回流焊后、TCG 100/500/850/2000次循环和HTS 200/500/1000小时,以监测密封剂的性能。

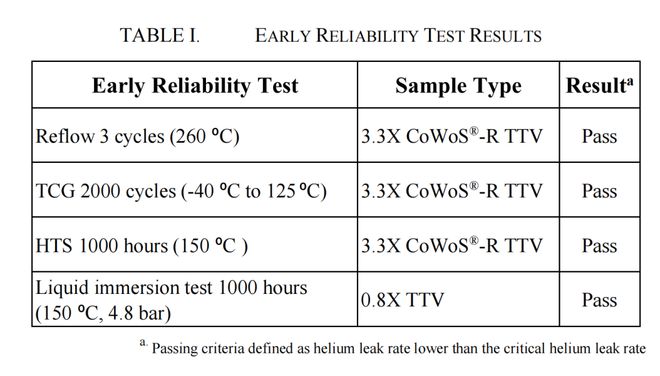

B. 早期可靠性测试结果

表 I 总结了 IMC-Si 集成 3.3X CoWoS-R 封装的早期可靠性测试结果。该集成封装成功通过了多次回流焊、TCG 和 HTS 测试,氦气泄漏率至少比 Qcr_He 低一个数量级。此外,如图 9 所示,我们在整个 TCG 和 HTS 测试过程中观察到稳定的氦气泄漏率,这表明密封剂在高温和长时间条件下具有良好的稳定性。TCG 测试中较大的温度变化以及由此引起的封装翘曲变化并未导致密封剂分层。通过 HTS 测试证实,在长时间的热机械应力作用下,密封剂与盖板和硅片之间仍保持着牢固的粘合力。

此外,我们还进行了一项加速测试,以评估密封剂在液体环境下的稳定性。将密封剂涂覆到单芯片测试载体上,并与金属盖板组装在一起。随后,将样品浸入150℃、4.8巴压力的去离子水中1000小时。这种严苛的环境旨在加速密封剂粘合性和完整性的任何化学降解。加速试验后的氦气泄漏测试结果远低于Qcr_He值一个数量级。这表明该密封剂在液态冷却剂中具有较长的使用寿命。

总结

我们首次在 CoWoS平台上集成了一种直接硅基液冷解决方案 IMC-Si。通过在硅芯片上应用抗翘曲且无泄漏的密封剂,液冷液能够流经硅芯片背面。集成的 3.3X CoWoS-R 封装能够散热高达 3.4 kW 的功率,功率密度可达 2.5 W/mm²。氦气泄漏测试和早期可靠性评估证实,该集成封装的氦气泄漏率始终低于临界阈值一个数量级,并通过了应力测试和液体浸没测试,且密封剂未发生劣化。

这些结果凸显了集成在 CoWoS 平台上的 IMC-Si 在严苛环境下可靠应用的潜力和可扩展性,它能够有效防止液体泄漏,并确保较长的使用寿命。未来的工作将着重于优化微柱设计并减少翘曲,以提高冷却效率。